Matrox Solios eCL/XCL dual-Base/single-Medium and cCL/XCL-F connectors and signal names

- See also

Previous

Previous

- Next

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO7 on M_DEV0 ( P0_OPTO_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV0 ( P0_TTL_AUX_IO_0 ).

-

M_AUX_IO10 on M_DEV0 ( P0_LVDS_AUX_IN0 ).

-

M_AUX_IO0 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN0 ).

-

M_AUX_IO1 on M_DEV0 and M_DEV1 ( OPTO_AUX_IN1 ).

-

M_AUX_IO2 on M_DEV0 and M_DEV1 ( TTL_AUX_IO_0 ).

-

M_AUX_IO4 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN0 ).

-

M_AUX_IO5 on M_DEV0 and M_DEV1 ( LVDS_AUX_IN1 ).

-

M_AUX_IO8 on M_DEV1 ( P1_TTL_AUX_IO_0 ).

This section serves as a reference to match Matrox Solios eCL/XCL dual-Base/single-Medium's and eCL/XCL-F's connectors and auxiliary/camera control signals with MIL information, such as MIL auxiliary/camera control signal numbers. To set/inquire all the settings for this board's auxiliary/camera control signals (for example, signal routing and timer settings), use MdigControl() / MdigInquire(), respectively.

Matrox Solios eCL/XCL dual-Base/single-Medium and eCL/XCL-F have a different number of acquisition paths and auxiliary/camera control signals. For each Matrox Solios eCL/XCL specified below, only the auxiliary/camera control signals associated with the following digitizer device numbers are supported:

|

Matrox Solios type |

Digitizer device # |

|

Matrox Solios eCL/XCL dual-Base |

|

|

Matrox Solios eCL/XCL single-Medium and Matrox Solios eCL/XCL-F |

The following table lists the connectors of the auxiliary/control signals that can be used for each digitizer device number:

|

Digitizer device # |

Matrox Solios eCL/XCL dual-Base and Matrox Solios eCL/XCL-F |

Matrox Solios eCL/XCL single-Medium |

|

External auxiliary I/O connector 0 and 1, and Camera Link video input connector (MDR0). |

External auxiliary I/O connector 0 and 1, and Camera Link video input connector (MDR0), |

|

|

External auxiliary I/O connector 0 and Camera Link video input connector (MDR1). |

Auxiliary I/O signals and camera control signals can have one or more functionalities (for example, trigger input, timer output, or user output, depending on the signal). Their possible functionalities are described in their description in the pinout table below. Shared input and output signals can be accessed by the digitizers with the specified M_DEV... number. Although a shared signal can be accessed by multiple digitizers, all the functionalities supported by the signal might not be accessible by all these digitizers. In the case of shared output signals, ensure that only one digitizer is driving the output.

Matrox Solios eCL/XCL dual-base/single-Medium and eCL/XCL-F have 4 trigger controllers per acquisition path so that on-board events (for example, acquisition and timer output) can start upon different triggers if required. Although a trigger controller might support several trigger input signals, only one signal can drive a trigger controller at any given time. For example, if you set signal A as the trigger input source for acquisition, and signal B as the trigger input source for timer 1, signal A and B must be driving different trigger controllers; if they drive the same trigger controller, an error is generated. Note that you can set a signal (for example, signal A) as the trigger input source for both acquisition and timer 1; in this case, the associated trigger controller triggers both events at the same time.

Only those auxiliary/camera control signals that have matching MIL information are included in this section. For information on internal connectors and a comprehensive list of all available input and output signals, refer to the board's installation and hardware reference manual.

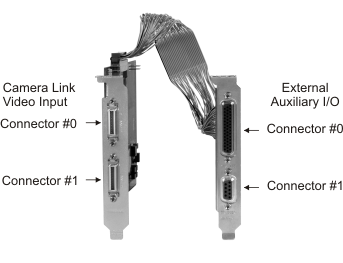

Board connectors

On the Matrox Solios eCL/XCL dual-Base/single-Medium and eCL/XCL-F boards, there are several interface connectors. On their bracket, there are two Camera Link video input connectors. On the bracket of their adapter board, there are two external auxiliary I/O connectors (DBHD-44 and DB-9); these allow you to access the signals of the internal auxiliary I/O connector from outside the computer enclosure.

All of Matrox Solios eCL/XCL dual-Base/single-Medium's and eCL/XCL-F's connectors have auxiliary/camera control signals with matching MIL information.

|

Connector Name |

Connector Abbreviation |

Image |

Description |

|

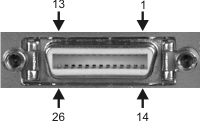

Camera Link video input connectors |

MDR (0 and 1) |

|

The two Camera Link video input connectors are 26-pin high-density D ribbon connectors. They are used to receive video input, timing, and synchronization signals and transmit/receive communication signals between the video source and the frame grabber. |

|

External auxiliary I/O connector 0 |

DBHD-44 |

|

External auxiliary I/O connector 0 is a high-density D-subminiature 44-pin female connector. It is used to transmit timing and synchronization signals, and transmit/receive auxiliary signals. It is located on the adapter board, interfacing with the internal 50-pin auxiliary I/O connector on the main board. |

|

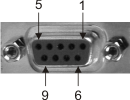

External auxiliary I/O connector 1 |

DB-9 |

|

External auxiliary I/O connector 1 is a standard D-subminiature 9-pin female connector. It is used to transmit/receive auxiliary signals. It is located on the adapter board, interfacing with the internal 50-pin auxiliary I/O connector on the main board. |

Signal names and their matching MIL constants

The table below lists the auxiliary/camera control signals with their associated MIL information. Note that the MIL constants in this table are those to use with MIL 10 and later. If you are upgrading from a previous version of MIL, you should port your code using the conversion tables for the Matrox Solios eCL/XCL (MILSoliosCameraLinkIOConversionTable) in the MIL release notes.

|

|

Description | ||

| MIL I/O # | |||

| Pin information | |||

| Direction | |||

| User-bit information | |||

| Trigger information | |||

| Timer information | |||

| Hardware manual signal name | |||

|

Indicates the following. (summarize)Indicates the following. (more details...) |

|||

Shared with: M_DEV1 |

Opto-isolated auxiliary signal (input), shared between both acquisition paths for trigger input or user input, and dedicated to acquisition path 1 for field polarity input. (summarize)Opto-isolated auxiliary signal (input), shared between both acquisition paths for trigger input or user input, and dedicated to acquisition path 1 for field polarity input. (more details...) |

||

| Pin information | Connector: DBHD-44 Pin: 24+, 8- | ||

| Direction |

Input |

||

| Trigger information | Trigger controller: 2 on acq

path 0; 2 or 0 on acq path 1. M_HARDWARE_PORT0; Digitizer device #: M_DEV0, M_DEV1; Trigger controller: 2 on acq path 0; 2 or 0 on acq path 1. |

||

| Hardware manual signal name | OPTO_AUX_IN0 | ||

Shared with: M_DEV1 |

Opto-isolated auxiliary signal (input), shared between both acquisition paths for trigger input or user input. (summarize)Opto-isolated auxiliary signal (input), shared between both acquisition paths for trigger input or user input. (more details...) |

||

| Pin information | Connector: DBHD-44 Pin: 38+, 39- | ||

| Direction |

Input |

||

| Trigger information | Trigger controller: 3 on acq

path 0; 3 or 1 on acq path 1. M_HARDWARE_PORT1; Digitizer device #: M_DEV0, M_DEV1; Trigger controller: 3 on acq path 0; 3 or 1 on acq path 1. |

||

| Hardware manual signal name | OPTO_AUX_IN1 | ||

Shared with: M_DEV1 |

TTL auxiliary signal (input/output), shared between both acquisition paths for trigger input or user input/output, and dedicated to acquisition path 0 for timer output. (summarize)TTL auxiliary signal (input/output), shared between both acquisition paths for trigger input or user input/output, and dedicated to acquisition path 0 for timer output. (more details...) |

||

| Pin information | Connector: DBHD-44 Pin: 43 | ||

| Direction |

Input/Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT4;

Digitizer device #: M_DEV0,

M_DEV1; (Hardware manual user signal rank 1 : 4 on acq path 0 ; 7 on acq path 1

)

|

||

| Trigger information | Trigger controller: 2 on acq

path 0; 2 on acq path 1. M_HARDWARE_PORT2; Digitizer device #: M_DEV0, M_DEV1; Trigger controller: 2 on acq path 0; 2 on acq path 1. |

||

| Timer information | Timer: M_TIMER2; Digitizer device #: M_DEV0; | ||

| Hardware manual signal name | TTL_AUX_IO_0 | ||

Shared with: M_DEV1 |

TTL auxiliary signal (input/output), shared between both acquisition paths for trigger input or user input/output, and dedicated to acquisition path 1 for timer output. (summarize)TTL auxiliary signal (input/output), shared between both acquisition paths for trigger input or user input/output, and dedicated to acquisition path 1 for timer output. (more details...) |

||

| Pin information | Connector: DBHD-44 Pin: 15 | ||

| Direction |

Input/Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT5;

Digitizer device #: M_DEV0,

M_DEV1; (Hardware manual user signal rank 1 : 7 on acq path 0 ; 4 on acq path 1

)

|

||

| Trigger information | Trigger controller: 3 on acq

path 0; 3 on acq path 1. M_HARDWARE_PORT3; Digitizer device #: M_DEV0, M_DEV1; Trigger controller: 3 on acq path 0; 3 on acq path 1. |

||

| Timer information | Timer: M_TIMER2; Digitizer device #: M_DEV1; | ||

| Hardware manual signal name | TTL_AUX_IO_1 | ||

Shared with: M_DEV1 |

LVDS auxiliary signal (input), shared between both acquisition paths for trigger input or user input, and dedicated to acquisition path 1 for field polarity input or quadrature input bit 0. (summarize)LVDS auxiliary signal (input), shared between both acquisition paths for trigger input or user input, and dedicated to acquisition path 1 for field polarity input or quadrature input bit 0. (more details...) |

||

| Pin information | Connector: DBHD-44 Pin: 32+, 31- | ||

| Direction |

Input |

||

| Trigger information | Trigger controller: 2 on acq

path 0; 2 or 0 on acq path 1. M_HARDWARE_PORT4; Digitizer device #: M_DEV0, M_DEV1; Trigger controller: 2 on acq path 0; 2 or 0 on acq path 1. |

||

| Hardware manual signal name | LVDS_AUX_IN0 | ||

Shared with: M_DEV1 |

LVDS auxiliary signal (input), shared between both acquisition paths for trigger input or user input, and dedicated to acquisition path 1 for timer clock input or quadrature input bit 1. (summarize)LVDS auxiliary signal (input), shared between both acquisition paths for trigger input or user input, and dedicated to acquisition path 1 for timer clock input or quadrature input bit 1. (more details...) |

||

| Pin information | Connector: DBHD-44 Pin: 12+, 28- | ||

| Direction |

Input |

||

| Trigger information | Trigger controller: 3 on acq

path 0; 3 or 1 on acq path 1. M_HARDWARE_PORT5; Digitizer device #: M_DEV0, M_DEV1; Trigger controller: 3 on acq path 0; 3 or 1 on acq path 1. |

||

| Hardware manual signal name | LVDS_AUX_IN1 | ||

|

Opto-isolated auxiliary signal (input) for acquisition path 0, which supports: trigger input, user input, or field polarity input. (summarize)Opto-isolated auxiliary signal (input) for acquisition path 0, which supports: trigger input, user input, or field polarity input. (more details...) |

|||

| Pin information | Connector: DB-9 Pin: 7+, 2- | ||

| Direction |

Input |

||

| Trigger information | Trigger controller: 0 on acq

path 0. M_HARDWARE_PORT6; Digitizer device #: M_DEV0; Trigger controller: 0 on acq path 0. |

||

| Hardware manual signal name | P0_OPTO_AUX_IN0 | ||

|

Opto-isolated auxiliary signal (input) for acquisition path 0, which supports: trigger input or user input. (summarize)Opto-isolated auxiliary signal (input) for acquisition path 0, which supports: trigger input or user input. (more details...) |

|||

| Pin information | Connector: DB-9 Pin: 4+, 5- | ||

| Direction |

Input |

||

| Trigger information | Trigger controller: 1 on acq

path 0. M_HARDWARE_PORT7; Digitizer device #: M_DEV0; Trigger controller: 1 on acq path 0. |

||

| Hardware manual signal name | P0_OPTO_AUX_IN1 | ||

|

TTL auxiliary signal (input/output) for acquisition path 0, which supports: timer output, trigger input, user input/output, or field polarity input. (summarize)TTL auxiliary signal (input/output) for acquisition path 0, which supports: timer output, trigger input, user input/output, or field polarity input. (more details...) |

|||

| Pin information | Connector: DB-9 Pin: 1 | ||

| Direction |

Input/Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT2;

Digitizer device #: M_DEV0;

(Hardware manual user signal rank 1 : 2 on acq path 0 )

|

||

| Trigger information | Trigger controller: 0 on acq

path 0. M_HARDWARE_PORT8; Digitizer device #: M_DEV0; Trigger controller: 0 on acq path 0. |

||

| Timer information | Timer: M_TIMER3; Digitizer device #: M_DEV0; | ||

| Hardware manual signal name | P0_TTL_AUX_IO_0 | ||

|

TTL auxiliary signal (input/output) for acquisition path 0, which supports: timer output, trigger input, or user input/output. (summarize)TTL auxiliary signal (input/output) for acquisition path 0, which supports: timer output, trigger input, or user input/output. (more details...) |

|||

| Pin information | Connector: DBHD-44 Pin: 13 | ||

| Direction |

Input/Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT3;

Digitizer device #: M_DEV0;

(Hardware manual user signal rank 1 : 3 on acq path 0 )

|

||

| Trigger information | Trigger controller: 1 on acq

path 0. M_HARDWARE_PORT9; Digitizer device #: M_DEV0; Trigger controller: 1 on acq path 0. |

||

| Timer information | Timer: M_TIMER1/M_TIMER4; Digitizer device #: M_DEV0; | ||

| Hardware manual signal name | P0_TTL_AUX_IO_1 | ||

|

LVDS auxiliary signal (input) for acquisition path 0, which supports: trigger input, user input, field polarity input, or quadrature input bit 0. (summarize)LVDS auxiliary signal (input) for acquisition path 0, which supports: trigger input, user input, field polarity input, or quadrature input bit 0. (more details...) |

|||

| Pin information | Connector: DB-9 Pin: 8+, 3- | ||

| Direction |

Input |

||

| Trigger information | Trigger controller: 0 on acq

path 0. M_HARDWARE_PORT10; Digitizer device #: M_DEV0; Trigger controller: 0 on acq path 0. |

||

| Hardware manual signal name | P0_LVDS_AUX_IN0 | ||

|

LVDS auxiliary signal (input) for acquisition path 0, which supports: trigger input, user input, timer clock input, or quadrature input bit 1. (summarize)LVDS auxiliary signal (input) for acquisition path 0, which supports: trigger input, user input, timer clock input, or quadrature input bit 1. (more details...) |

|||

| Pin information | Connector: DBHD-44 Pin: 37+, 23- | ||

| Direction |

Input |

||

| Trigger information | Trigger controller: 1 on acq

path 0. M_HARDWARE_PORT11; Digitizer device #: M_DEV0; Trigger controller: 1 on acq path 0. |

||

| Hardware manual signal name | P0_LVDS_AUX_IN1 | ||

|

LVDS auxiliary signal (output) for acquisition path 0, which supports: timer output or user output. (summarize)LVDS auxiliary signal (output) for acquisition path 0, which supports: timer output or user output. (more details...) |

|||

| Pin information | Connector: DBHD-44 Pin: 20+, 4- | ||

| Direction |

Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT0;

Digitizer device #: M_DEV0;

(Hardware manual user signal rank 1 : 5 on acq path 0 )

|

||

| Timer information | Timer: M_TIMER1; Digitizer device #: M_DEV0; | ||

| Hardware manual signal name | P0_LVDS_AUX_OUT0 | ||

|

LVDS auxiliary signal (output) for acquisition path 0, which supports: timer output or user output. (summarize)LVDS auxiliary signal (output) for acquisition path 0, which supports: timer output or user output. (more details...) |

|||

| Pin information | Connector: DBHD-44 Pin: 19+, 3- | ||

| Direction |

Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT1;

Digitizer device #: M_DEV0;

(Hardware manual user signal rank 1 : 6 on acq path 0 )

|

||

| Timer information | Timer: M_TIMER2; Digitizer device #: M_DEV0; | ||

| Hardware manual signal name | P0_LVDS_AUX_OUT1 | ||

|

Camera control output 1 for acquisition path 0, which supports: timer output, user output, VSYNC, HSYNC, clock output, or rerouting of specific auxiliary input signals. Only the following auxiliary input signals can be rerouted to this output signal: Camera control output 1 for acquisition path 0, which supports: timer output, user output, VSYNC, HSYNC, clock output, or rerouting of specific auxiliary input signals. (more details...) |

|||

| Pin information | Connector: MDR (0) Pin: 5+, 18- | ||

| Direction |

Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT_CC_IO0/M_USER_BIT_CC_IO1;

Digitizer device #: M_DEV0;

|

||

| Timer information | Timer: M_TIMER1/M_TIMER2; Digitizer device #: M_DEV0; | ||

| Hardware manual signal name | CC1 (0) | ||

|

Camera control output 2 for acquisition path 0, which supports: timer output, user output, VSYNC, HSYNC, clock output, or rerouting of specific auxiliary input signals. Only the following auxiliary input signals can be rerouted to this output signal: Camera control output 2 for acquisition path 0, which supports: timer output, user output, VSYNC, HSYNC, clock output, or rerouting of specific auxiliary input signals. (more details...) |

|||

| Pin information | Connector: MDR (0) Pin: 17+, 4- | ||

| Direction |

Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT_CC_IO0/M_USER_BIT_CC_IO1;

Digitizer device #: M_DEV0;

|

||

| Timer information | Timer: M_TIMER1/M_TIMER2; Digitizer device #: M_DEV0; | ||

| Hardware manual signal name | CC2 (0) | ||

|

Camera control output 3 for acquisition path 0, which supports: timer output, user output, VSYNC, HSYNC, clock output, or rerouting of specific auxiliary input signals. Only the following auxiliary input signals can be rerouted to this output signal: Camera control output 3 for acquisition path 0, which supports: timer output, user output, VSYNC, HSYNC, clock output, or rerouting of specific auxiliary input signals. (more details...) |

|||

| Pin information | Connector: MDR (0) Pin: 3+, 16- | ||

| Direction |

Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT_CC_IO0/M_USER_BIT_CC_IO1;

Digitizer device #: M_DEV0;

|

||

| Timer information | Timer: M_TIMER1/M_TIMER2; Digitizer device #: M_DEV0; | ||

| Hardware manual signal name | CC3 (0) | ||

|

Camera control output 4 for acquisition path 0, which supports: timer output, user output, VSYNC, HSYNC, clock output, or rerouting of specific auxiliary input signals. Only the following auxiliary input signals can be rerouted to this output signal: Camera control output 4 for acquisition path 0, which supports: timer output, user output, VSYNC, HSYNC, clock output, or rerouting of specific auxiliary input signals. (more details...) |

|||

| Pin information | Connector: MDR (0) Pin: 15+, 2- | ||

| Direction |

Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT_CC_IO0/M_USER_BIT_CC_IO1;

Digitizer device #: M_DEV0;

|

||

| Timer information | Timer: M_TIMER1/M_TIMER2; Digitizer device #: M_DEV0; | ||

| Hardware manual signal name | CC4 (0) | ||

|

Indicates the following. (summarize)Indicates the following. (more details...) |

|||

Shared with: M_DEV0 |

Opto-isolated auxiliary signal (input), shared between both acquisition paths for trigger input or user input, and dedicated to acquisition path 1 for field polarity input. (summarize)Opto-isolated auxiliary signal (input), shared between both acquisition paths for trigger input or user input, and dedicated to acquisition path 1 for field polarity input. (more details...) |

||

| Pin information | Connector: DBHD-44 Pin: 24+, 8- | ||

| Direction |

Input |

||

| Trigger information | Trigger controller: 2 on acq

path 0; 2 or 0 on acq path 1. M_HARDWARE_PORT0; Digitizer device #: M_DEV0, M_DEV1; Trigger controller: 2 on acq path 0; 2 or 0 on acq path 1. |

||

| Hardware manual signal name | OPTO_AUX_IN0 | ||

Shared with: M_DEV0 |

Opto-isolated auxiliary signal (input), shared between both acquisition paths for trigger input or user input. (summarize)Opto-isolated auxiliary signal (input), shared between both acquisition paths for trigger input or user input. (more details...) |

||

| Pin information | Connector: DBHD-44 Pin: 38+, 39- | ||

| Direction |

Input |

||

| Trigger information | Trigger controller: 3 on acq

path 0; 3 or 1 on acq path 1. M_HARDWARE_PORT1; Digitizer device #: M_DEV0, M_DEV1; Trigger controller: 3 on acq path 0; 3 or 1 on acq path 1. |

||

| Hardware manual signal name | OPTO_AUX_IN1 | ||

Shared with: M_DEV0 |

TTL auxiliary signal (input/output), shared between both acquisition paths for trigger input or user input/output, and dedicated to acquisition path 0 for timer output. (summarize)TTL auxiliary signal (input/output), shared between both acquisition paths for trigger input or user input/output, and dedicated to acquisition path 0 for timer output. (more details...) |

||

| Pin information | Connector: DBHD-44 Pin: 43 | ||

| Direction |

Input/Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT4;

Digitizer device #: M_DEV0,

M_DEV1; (Hardware manual user signal rank 1 : 4 on acq path 0 ; 7 on acq path 1

)

|

||

| Trigger information | Trigger controller: 2 on acq

path 0; 2 on acq path 1. M_HARDWARE_PORT2; Digitizer device #: M_DEV0, M_DEV1; Trigger controller: 2 on acq path 0; 2 on acq path 1. |

||

| Timer information | Timer: M_TIMER2; Digitizer device #: M_DEV0; | ||

| Hardware manual signal name | TTL_AUX_IO_0 | ||

Shared with: M_DEV0 |

TTL auxiliary signal (input/output), shared between both acquisition paths for trigger input or user input/output, and dedicated to acquisition path 1 for timer output. (summarize)TTL auxiliary signal (input/output), shared between both acquisition paths for trigger input or user input/output, and dedicated to acquisition path 1 for timer output. (more details...) |

||

| Pin information | Connector: DBHD-44 Pin: 15 | ||

| Direction |

Input/Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT5;

Digitizer device #: M_DEV0,

M_DEV1; (Hardware manual user signal rank 1 : 7 on acq path 0 ; 4 on acq path 1

)

|

||

| Trigger information | Trigger controller: 3 on acq

path 0; 3 on acq path 1. M_HARDWARE_PORT3; Digitizer device #: M_DEV0, M_DEV1; Trigger controller: 3 on acq path 0; 3 on acq path 1. |

||

| Timer information | Timer: M_TIMER2; Digitizer device #: M_DEV1; | ||

| Hardware manual signal name | TTL_AUX_IO_1 | ||

Shared with: M_DEV0 |

LVDS auxiliary signal (input), shared between both acquisition paths for trigger input or user input, and dedicated to acquisition path 1 for field polarity input or quadrature input bit 0. (summarize)LVDS auxiliary signal (input), shared between both acquisition paths for trigger input or user input, and dedicated to acquisition path 1 for field polarity input or quadrature input bit 0. (more details...) |

||

| Pin information | Connector: DBHD-44 Pin: 32+, 31- | ||

| Direction |

Input |

||

| Trigger information | Trigger controller: 2 on acq

path 0; 2 or 0 on acq path 1. M_HARDWARE_PORT4; Digitizer device #: M_DEV0, M_DEV1; Trigger controller: 2 on acq path 0; 2 or 0 on acq path 1. |

||

| Hardware manual signal name | LVDS_AUX_IN0 | ||

Shared with: M_DEV0 |

LVDS auxiliary signal (input), shared between both acquisition paths for trigger input or user input, and dedicated to acquisition path 1 for timer clock input or quadrature input bit 1. (summarize)LVDS auxiliary signal (input), shared between both acquisition paths for trigger input or user input, and dedicated to acquisition path 1 for timer clock input or quadrature input bit 1. (more details...) |

||

| Pin information | Connector: DBHD-44 Pin: 12+, 28- | ||

| Direction |

Input |

||

| Trigger information | Trigger controller: 3 on acq

path 0; 3 or 1 on acq path 1. M_HARDWARE_PORT5; Digitizer device #: M_DEV0, M_DEV1; Trigger controller: 3 on acq path 0; 3 or 1 on acq path 1. |

||

| Hardware manual signal name | LVDS_AUX_IN1 | ||

|

TTL auxiliary signal (input/output) for acquisition path 1, which supports: timer output, trigger input, user input/output, or field polarity input. (summarize)TTL auxiliary signal (input/output) for acquisition path 1, which supports: timer output, trigger input, user input/output, or field polarity input. (more details...) |

|||

| Pin information | Connector: DBHD-44 Pin: 35 | ||

| Direction |

Input/Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT2;

Digitizer device #: M_DEV1;

(Hardware manual user signal rank 1 : 2 on acq path 1 )

|

||

| Trigger information | Trigger controller: 0 on acq

path 1. M_HARDWARE_PORT8; Digitizer device #: M_DEV1; Trigger controller: 0 on acq path 1. |

||

| Timer information | Timer: M_TIMER3; Digitizer device #: M_DEV1; | ||

| Hardware manual signal name | P1_TTL_AUX_IO_0 | ||

|

TTL auxiliary signal (input/output) for acquisition path 1, which supports: timer output, trigger input, or user input/output. (summarize)TTL auxiliary signal (input/output) for acquisition path 1, which supports: timer output, trigger input, or user input/output. (more details...) |

|||

| Pin information | Connector: DBHD-44 Pin: 1 | ||

| Direction |

Input/Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT3;

Digitizer device #: M_DEV1;

(Hardware manual user signal rank 1 : 3 on acq path 1 )

|

||

| Trigger information | Trigger controller: 1 on acq

path 1. M_HARDWARE_PORT9; Digitizer device #: M_DEV1; Trigger controller: 1 on acq path 1. |

||

| Timer information | Timer: M_TIMER1; Digitizer device #: M_DEV1; | ||

| Hardware manual signal name | P1_TTL_AUX_IO_1 | ||

|

LVDS auxiliary signal (output) for acquisition path 1, which supports: timer output or user output. (summarize)LVDS auxiliary signal (output) for acquisition path 1, which supports: timer output or user output. (more details...) |

|||

| Pin information | Connector: DBHD-44 Pin: 33+, 18- | ||

| Direction |

Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT0;

Digitizer device #: M_DEV1;

(Hardware manual user signal rank 1 : 5 on acq path 1 )

|

||

| Timer information | Timer: M_TIMER1; Digitizer device #: M_DEV1; | ||

| Hardware manual signal name | P1_LVDS_AUX_OUT0 | ||

|

LVDS auxiliary signal (output) for acquisition path 1, which supports: timer output or user output. (summarize)LVDS auxiliary signal (output) for acquisition path 1, which supports: timer output or user output. (more details...) |

|||

| Pin information | Connector: DBHD-44 Pin: 2+, 17- | ||

| Direction |

Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT1;

Digitizer device #: M_DEV1;

(Hardware manual user signal rank 1 : 6 on acq path 1 )

|

||

| Timer information | Timer: M_TIMER2; Digitizer device #: M_DEV1; | ||

| Hardware manual signal name | P1_LVDS_AUX_OUT1 | ||

|

Camera control output 1 for acquisition path 1, which supports: timer output, user output, VSYNC, HSYNC, clock output, or rerouting of specific auxiliary input signals. Only the following auxiliary input signals can be rerouted to this output signal: Camera control output 1 for acquisition path 1, which supports: timer output, user output, VSYNC, HSYNC, clock output, or rerouting of specific auxiliary input signals. (more details...) |

|||

| Pin information | Connector: MDR (1) Pin: 5+, 18- | ||

| Direction |

Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT_CC_IO0/M_USER_BIT_CC_IO1;

Digitizer device #: M_DEV1;

|

||

| Timer information | Timer: M_TIMER1/M_TIMER2; Digitizer device #: M_DEV1; | ||

| Hardware manual signal name | CC1 (1) | ||

|

Camera control output 2 for acquisition path 1, which supports: timer output, user output, VSYNC, HSYNC, clock output, or rerouting of specific auxiliary input signals. Only the following auxiliary input signals can be rerouted to this output signal: Camera control output 2 for acquisition path 1, which supports: timer output, user output, VSYNC, HSYNC, clock output, or rerouting of specific auxiliary input signals. (more details...) |

|||

| Pin information | Connector: MDR (1) Pin: 17+, 4- | ||

| Direction |

Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT_CC_IO0/M_USER_BIT_CC_IO1;

Digitizer device #: M_DEV1;

|

||

| Timer information | Timer: M_TIMER1/M_TIMER2; Digitizer device #: M_DEV1; | ||

| Hardware manual signal name | CC2 (1) | ||

|

Camera control output 3 for acquisition path 1, which supports: timer output, user output, VSYNC, HSYNC, clock output, or rerouting of specific auxiliary input signals. Only the following auxiliary input signals can be rerouted to this output signal: Camera control output 3 for acquisition path 1, which supports: timer output, user output, VSYNC, HSYNC, clock output, or rerouting of specific auxiliary input signals. (more details...) |

|||

| Pin information | Connector: MDR (1) Pin: 3+, 16- | ||

| Direction |

Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT_CC_IO0/M_USER_BIT_CC_IO1;

Digitizer device #: M_DEV1;

|

||

| Timer information | Timer: M_TIMER1/M_TIMER2; Digitizer device #: M_DEV1; | ||

| Hardware manual signal name | CC3 (1) | ||

|

Camera control output 4 for acquisition path 1, which supports: timer output, user output, VSYNC, HSYNC, clock output, or rerouting of specific auxiliary input signals. Only the following auxiliary input signals can be rerouted to this output signal: Camera control output 4 for acquisition path 1, which supports: timer output, user output, VSYNC, HSYNC, clock output, or rerouting of specific auxiliary input signals. (more details...) |

|||

| Pin information | Connector: MDR (1) Pin: 15+, 2- | ||

| Direction |

Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT_CC_IO0/M_USER_BIT_CC_IO1;

Digitizer device #: M_DEV1;

|

||

| Timer information | Timer: M_TIMER1/M_TIMER2; Digitizer device #: M_DEV1; | ||

| Hardware manual signal name | CC4 (1) | ||

|

|

Description | ||

| MIL I/O # | |||

| Pin information | |||

| Direction | |||

| User-bit information | |||

| Trigger information | |||

| Timer information | |||

| Hardware manual signal name | |||

|

Indicates the following. (summarize)Indicates the following. (more details...) |

|||

Shared with: M_DEV1 |

Opto-isolated auxiliary signal (input), shared between both acquisition paths for trigger input or user input, and dedicated to acquisition path 1 for field polarity input. (summarize)Opto-isolated auxiliary signal (input), shared between both acquisition paths for trigger input or user input, and dedicated to acquisition path 1 for field polarity input. (more details...) |

||

| Pin information | Connector: DBHD-44 Pin: 24+, 8- | ||

| Direction |

Input |

||

| Trigger information | Trigger controller: 2 on acq

path 0; 2 or 0 on acq path 1. M_HARDWARE_PORT0; Digitizer device #: M_DEV0, M_DEV1; Trigger controller: 2 on acq path 0; 2 or 0 on acq path 1. |

||

| Hardware manual signal name | OPTO_AUX_IN0 | ||

Shared with: M_DEV1 |

Opto-isolated auxiliary signal (input), shared between both acquisition paths for trigger input or user input. (summarize)Opto-isolated auxiliary signal (input), shared between both acquisition paths for trigger input or user input. (more details...) |

||

| Pin information | Connector: DBHD-44 Pin: 38+, 39- | ||

| Direction |

Input |

||

| Trigger information | Trigger controller: 3 on acq

path 0; 3 or 1 on acq path 1. M_HARDWARE_PORT1; Digitizer device #: M_DEV0, M_DEV1; Trigger controller: 3 on acq path 0; 3 or 1 on acq path 1. |

||

| Hardware manual signal name | OPTO_AUX_IN1 | ||

Shared with: M_DEV1 |

TTL auxiliary signal (input/output), shared between both acquisition paths for trigger input or user input/output, and dedicated to acquisition path 0 for timer output. (summarize)TTL auxiliary signal (input/output), shared between both acquisition paths for trigger input or user input/output, and dedicated to acquisition path 0 for timer output. (more details...) |

||

| Pin information | Connector: DBHD-44 Pin: 43 | ||

| Direction |

Input/Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT4;

Digitizer device #: M_DEV0,

M_DEV1; (Hardware manual user signal rank 1 : 4 on acq path 0 ; 7 on acq path 1

)

|

||

| Trigger information | Trigger controller: 2 on acq

path 0; 2 on acq path 1. M_HARDWARE_PORT2; Digitizer device #: M_DEV0, M_DEV1; Trigger controller: 2 on acq path 0; 2 on acq path 1. |

||

| Timer information | Timer: M_TIMER2; Digitizer device #: M_DEV0; | ||

| Hardware manual signal name | TTL_AUX_IO_0 | ||

Shared with: M_DEV1 |

TTL auxiliary signal (input/output), shared between both acquisition paths for trigger input or user input/output, and dedicated to acquisition path 1 for timer output. (summarize)TTL auxiliary signal (input/output), shared between both acquisition paths for trigger input or user input/output, and dedicated to acquisition path 1 for timer output. (more details...) |

||

| Pin information | Connector: DBHD-44 Pin: 15 | ||

| Direction |

Input/Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT5;

Digitizer device #: M_DEV0,

M_DEV1; (Hardware manual user signal rank 1 : 7 on acq path 0 ; 4 on acq path 1

)

|

||

| Trigger information | Trigger controller: 3 on acq

path 0; 3 on acq path 1. M_HARDWARE_PORT3; Digitizer device #: M_DEV0, M_DEV1; Trigger controller: 3 on acq path 0; 3 on acq path 1. |

||

| Timer information | Timer: M_TIMER2; Digitizer device #: M_DEV1; | ||

| Hardware manual signal name | TTL_AUX_IO_1 | ||

Shared with: M_DEV1 |

LVDS auxiliary signal (input), shared between both acquisition paths for trigger input or user input, and dedicated to acquisition path 1 for field polarity input or quadrature input bit 0. (summarize)LVDS auxiliary signal (input), shared between both acquisition paths for trigger input or user input, and dedicated to acquisition path 1 for field polarity input or quadrature input bit 0. (more details...) |

||

| Pin information | Connector: DBHD-44 Pin: 32+, 31- | ||

| Direction |

Input |

||

| Trigger information | Trigger controller: 2 on acq

path 0; 2 or 0 on acq path 1. M_HARDWARE_PORT4; Digitizer device #: M_DEV0, M_DEV1; Trigger controller: 2 on acq path 0; 2 or 0 on acq path 1. |

||

| Hardware manual signal name | LVDS_AUX_IN0 | ||

Shared with: M_DEV1 |

LVDS auxiliary signal (input), shared between both acquisition paths for trigger input or user input, and dedicated to acquisition path 1 for timer clock input or quadrature input bit 1. (summarize)LVDS auxiliary signal (input), shared between both acquisition paths for trigger input or user input, and dedicated to acquisition path 1 for timer clock input or quadrature input bit 1. (more details...) |

||

| Pin information | Connector: DBHD-44 Pin: 12+, 28- | ||

| Direction |

Input |

||

| Trigger information | Trigger controller: 3 on acq

path 0; 3 or 1 on acq path 1. M_HARDWARE_PORT5; Digitizer device #: M_DEV0, M_DEV1; Trigger controller: 3 on acq path 0; 3 or 1 on acq path 1. |

||

| Hardware manual signal name | LVDS_AUX_IN1 | ||

|

Opto-isolated auxiliary signal (input) for acquisition path 0, which supports: trigger input, user input, or field polarity input. (summarize)Opto-isolated auxiliary signal (input) for acquisition path 0, which supports: trigger input, user input, or field polarity input. (more details...) |

|||

| Pin information | Connector: DB-9 Pin: 7+, 2- | ||

| Direction |

Input |

||

| Trigger information | Trigger controller: 0 on acq

path 0. M_HARDWARE_PORT6; Digitizer device #: M_DEV0; Trigger controller: 0 on acq path 0. |

||

| Hardware manual signal name | P0_OPTO_AUX_IN0 | ||

|

Opto-isolated auxiliary signal (input) for acquisition path 0, which supports: trigger input or user input. (summarize)Opto-isolated auxiliary signal (input) for acquisition path 0, which supports: trigger input or user input. (more details...) |

|||

| Pin information | Connector: DB-9 Pin: 4+, 5- | ||

| Direction |

Input |

||

| Trigger information | Trigger controller: 1 on acq

path 0. M_HARDWARE_PORT7; Digitizer device #: M_DEV0; Trigger controller: 1 on acq path 0. |

||

| Hardware manual signal name | P0_OPTO_AUX_IN1 | ||

|

TTL auxiliary signal (input/output) for acquisition path 0, which supports: timer output, trigger input, user input/output, or field polarity input. (summarize)TTL auxiliary signal (input/output) for acquisition path 0, which supports: timer output, trigger input, user input/output, or field polarity input. (more details...) |

|||

| Pin information | Connector: DB-9 Pin: 1 | ||

| Direction |

Input/Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT2;

Digitizer device #: M_DEV0;

(Hardware manual user signal rank 1 : 2 on acq path 0 )

|

||

| Trigger information | Trigger controller: 0 on acq

path 0. M_HARDWARE_PORT8; Digitizer device #: M_DEV0; Trigger controller: 0 on acq path 0. |

||

| Timer information | Timer: M_TIMER3; Digitizer device #: M_DEV0; | ||

| Hardware manual signal name | P0_TTL_AUX_IO_0 | ||

|

TTL auxiliary signal (input/output) for acquisition path 0, which supports: timer output, trigger input, or user input/output. (summarize)TTL auxiliary signal (input/output) for acquisition path 0, which supports: timer output, trigger input, or user input/output. (more details...) |

|||

| Pin information | Connector: DBHD-44 Pin: 13 | ||

| Direction |

Input/Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT3;

Digitizer device #: M_DEV0;

(Hardware manual user signal rank 1 : 3 on acq path 0 )

|

||

| Trigger information | Trigger controller: 1 on acq

path 0. M_HARDWARE_PORT9; Digitizer device #: M_DEV0; Trigger controller: 1 on acq path 0. |

||

| Timer information | Timer: M_TIMER1/M_TIMER4; Digitizer device #: M_DEV0; | ||

| Hardware manual signal name | P0_TTL_AUX_IO_1 | ||

|

LVDS auxiliary signal (input) for acquisition path 0, which supports: trigger input, user input, field polarity input, or quadrature input bit 0. (summarize)LVDS auxiliary signal (input) for acquisition path 0, which supports: trigger input, user input, field polarity input, or quadrature input bit 0. (more details...) |

|||

| Pin information | Connector: DB-9 Pin: 8+, 3- | ||

| Direction |

Input |

||

| Trigger information | Trigger controller: 0 on acq

path 0. M_HARDWARE_PORT10; Digitizer device #: M_DEV0; Trigger controller: 0 on acq path 0. |

||

| Hardware manual signal name | P0_LVDS_AUX_IN0 | ||

|

LVDS auxiliary signal (input) for acquisition path 0, which supports: trigger input, user input, timer clock input, or quadrature input bit 1. (summarize)LVDS auxiliary signal (input) for acquisition path 0, which supports: trigger input, user input, timer clock input, or quadrature input bit 1. (more details...) |

|||

| Pin information | Connector: DBHD-44 Pin: 37+, 23- | ||

| Direction |

Input |

||

| Trigger information | Trigger controller: 1 on acq

path 0. M_HARDWARE_PORT11; Digitizer device #: M_DEV0; Trigger controller: 1 on acq path 0. |

||

| Hardware manual signal name | P0_LVDS_AUX_IN1 | ||

|

Indicates the following. (summarize)Indicates the following. (more details...) |

|||

Shared with: M_DEV0 |

Opto-isolated auxiliary signal (input), shared between both acquisition paths for trigger input or user input, and dedicated to acquisition path 1 for field polarity input. (summarize)Opto-isolated auxiliary signal (input), shared between both acquisition paths for trigger input or user input, and dedicated to acquisition path 1 for field polarity input. (more details...) |

||

| Pin information | Connector: DBHD-44 Pin: 24+, 8- | ||

| Direction |

Input |

||

| Trigger information | Trigger controller: 2 on acq

path 0; 2 or 0 on acq path 1. M_HARDWARE_PORT0; Digitizer device #: M_DEV0, M_DEV1; Trigger controller: 2 on acq path 0; 2 or 0 on acq path 1. |

||

| Hardware manual signal name | OPTO_AUX_IN0 | ||

Shared with: M_DEV0 |

Opto-isolated auxiliary signal (input), shared between both acquisition paths for trigger input or user input. (summarize)Opto-isolated auxiliary signal (input), shared between both acquisition paths for trigger input or user input. (more details...) |

||

| Pin information | Connector: DBHD-44 Pin: 38+, 39- | ||

| Direction |

Input |

||

| Trigger information | Trigger controller: 3 on acq

path 0; 3 or 1 on acq path 1. M_HARDWARE_PORT1; Digitizer device #: M_DEV0, M_DEV1; Trigger controller: 3 on acq path 0; 3 or 1 on acq path 1. |

||

| Hardware manual signal name | OPTO_AUX_IN1 | ||

Shared with: M_DEV0 |

TTL auxiliary signal (input/output), shared between both acquisition paths for trigger input or user input/output, and dedicated to acquisition path 0 for timer output. (summarize)TTL auxiliary signal (input/output), shared between both acquisition paths for trigger input or user input/output, and dedicated to acquisition path 0 for timer output. (more details...) |

||

| Pin information | Connector: DBHD-44 Pin: 43 | ||

| Direction |

Input/Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT4;

Digitizer device #: M_DEV0,

M_DEV1; (Hardware manual user signal rank 1 : 4 on acq path 0 ; 7 on acq path 1

)

|

||

| Trigger information | Trigger controller: 2 on acq

path 0; 2 on acq path 1. M_HARDWARE_PORT2; Digitizer device #: M_DEV0, M_DEV1; Trigger controller: 2 on acq path 0; 2 on acq path 1. |

||

| Timer information | Timer: M_TIMER2; Digitizer device #: M_DEV0; | ||

| Hardware manual signal name | TTL_AUX_IO_0 | ||

Shared with: M_DEV0 |

TTL auxiliary signal (input/output), shared between both acquisition paths for trigger input or user input/output, and dedicated to acquisition path 1 for timer output. (summarize)TTL auxiliary signal (input/output), shared between both acquisition paths for trigger input or user input/output, and dedicated to acquisition path 1 for timer output. (more details...) |

||

| Pin information | Connector: DBHD-44 Pin: 15 | ||

| Direction |

Input/Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT5;

Digitizer device #: M_DEV0,

M_DEV1; (Hardware manual user signal rank 1 : 7 on acq path 0 ; 4 on acq path 1

)

|

||

| Trigger information | Trigger controller: 3 on acq

path 0; 3 on acq path 1. M_HARDWARE_PORT3; Digitizer device #: M_DEV0, M_DEV1; Trigger controller: 3 on acq path 0; 3 on acq path 1. |

||

| Timer information | Timer: M_TIMER2; Digitizer device #: M_DEV1; | ||

| Hardware manual signal name | TTL_AUX_IO_1 | ||

Shared with: M_DEV0 |

LVDS auxiliary signal (input), shared between both acquisition paths for trigger input or user input, and dedicated to acquisition path 1 for field polarity input or quadrature input bit 0. (summarize)LVDS auxiliary signal (input), shared between both acquisition paths for trigger input or user input, and dedicated to acquisition path 1 for field polarity input or quadrature input bit 0. (more details...) |

||

| Pin information | Connector: DBHD-44 Pin: 32+, 31- | ||

| Direction |

Input |

||

| Trigger information | Trigger controller: 2 on acq

path 0; 2 or 0 on acq path 1. M_HARDWARE_PORT4; Digitizer device #: M_DEV0, M_DEV1; Trigger controller: 2 on acq path 0; 2 or 0 on acq path 1. |

||

| Hardware manual signal name | LVDS_AUX_IN0 | ||

Shared with: M_DEV0 |

LVDS auxiliary signal (input), shared between both acquisition paths for trigger input or user input, and dedicated to acquisition path 1 for timer clock input or quadrature input bit 1. (summarize)LVDS auxiliary signal (input), shared between both acquisition paths for trigger input or user input, and dedicated to acquisition path 1 for timer clock input or quadrature input bit 1. (more details...) |

||

| Pin information | Connector: DBHD-44 Pin: 12+, 28- | ||

| Direction |

Input |

||

| Trigger information | Trigger controller: 3 on acq

path 0; 3 or 1 on acq path 1. M_HARDWARE_PORT5; Digitizer device #: M_DEV0, M_DEV1; Trigger controller: 3 on acq path 0; 3 or 1 on acq path 1. |

||

| Hardware manual signal name | LVDS_AUX_IN1 | ||

|

TTL auxiliary signal (input/output) for acquisition path 1, which supports: timer output, trigger input, user input/output, or field polarity input. (summarize)TTL auxiliary signal (input/output) for acquisition path 1, which supports: timer output, trigger input, user input/output, or field polarity input. (more details...) |

|||

| Pin information | Connector: DBHD-44 Pin: 35 | ||

| Direction |

Input/Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT2;

Digitizer device #: M_DEV1;

(Hardware manual user signal rank 1 : 2 on acq path 1 )

|

||

| Trigger information | Trigger controller: 0 on acq

path 1. M_HARDWARE_PORT8; Digitizer device #: M_DEV1; Trigger controller: 0 on acq path 1. |

||

| Timer information | Timer: M_TIMER3; Digitizer device #: M_DEV1; | ||

| Hardware manual signal name | P1_TTL_AUX_IO_0 | ||

|

TTL auxiliary signal (input/output) for acquisition path 1, which supports: timer output, trigger input, or user input/output. (summarize)TTL auxiliary signal (input/output) for acquisition path 1, which supports: timer output, trigger input, or user input/output. (more details...) |

|||

| Pin information | Connector: DBHD-44 Pin: 1 | ||

| Direction |

Input/Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT3;

Digitizer device #: M_DEV1;

(Hardware manual user signal rank 1 : 3 on acq path 1 )

|

||

| Trigger information | Trigger controller: 1 on acq

path 1. M_HARDWARE_PORT9; Digitizer device #: M_DEV1; Trigger controller: 1 on acq path 1. |

||

| Timer information | Timer: M_TIMER1; Digitizer device #: M_DEV1; | ||

| Hardware manual signal name | P1_TTL_AUX_IO_1 | ||

|

|

Description | ||

| MIL I/O # | |||

| Pin information | |||

| Direction | |||

| User-bit information | |||

| Trigger information | |||

| Timer information | |||

| Hardware manual signal name | |||

|

Indicates the following. (summarize)Indicates the following. (more details...) |

|||

Shared with: M_DEV1 |

TTL auxiliary signal (input/output), shared between both acquisition paths for trigger input or user input/output, and dedicated to acquisition path 0 for timer output. (summarize)TTL auxiliary signal (input/output), shared between both acquisition paths for trigger input or user input/output, and dedicated to acquisition path 0 for timer output. (more details...) |

||

| Pin information | Connector: DBHD-44 Pin: 43 | ||

| Direction |

Input/Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT4;

Digitizer device #: M_DEV0,

M_DEV1; (Hardware manual user signal rank 1 : 4 on acq path 0 ; 7 on acq path 1

)

|

||

| Trigger information | Trigger controller: 2 on acq

path 0; 2 on acq path 1. M_HARDWARE_PORT2; Digitizer device #: M_DEV0, M_DEV1; Trigger controller: 2 on acq path 0; 2 on acq path 1. |

||

| Timer information | Timer: M_TIMER2; Digitizer device #: M_DEV0; | ||

| Hardware manual signal name | TTL_AUX_IO_0 | ||

Shared with: M_DEV1 |

TTL auxiliary signal (input/output), shared between both acquisition paths for trigger input or user input/output, and dedicated to acquisition path 1 for timer output. (summarize)TTL auxiliary signal (input/output), shared between both acquisition paths for trigger input or user input/output, and dedicated to acquisition path 1 for timer output. (more details...) |

||

| Pin information | Connector: DBHD-44 Pin: 15 | ||

| Direction |

Input/Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT5;

Digitizer device #: M_DEV0,

M_DEV1; (Hardware manual user signal rank 1 : 7 on acq path 0 ; 4 on acq path 1

)

|

||

| Trigger information | Trigger controller: 3 on acq

path 0; 3 on acq path 1. M_HARDWARE_PORT3; Digitizer device #: M_DEV0, M_DEV1; Trigger controller: 3 on acq path 0; 3 on acq path 1. |

||

| Timer information | Timer: M_TIMER2; Digitizer device #: M_DEV1; | ||

| Hardware manual signal name | TTL_AUX_IO_1 | ||

|

TTL auxiliary signal (input/output) for acquisition path 0, which supports: timer output, trigger input, user input/output, or field polarity input. (summarize)TTL auxiliary signal (input/output) for acquisition path 0, which supports: timer output, trigger input, user input/output, or field polarity input. (more details...) |

|||

| Pin information | Connector: DB-9 Pin: 1 | ||

| Direction |

Input/Output |

||

| User-bit information |

MIL user-bit #: M_USER_BIT2;

Digitizer device #: M_DEV0;

(Hardware manual user signal rank 1 : 2 on acq path 0 )

|

||

| Trigger information | Trigger controller: 0 on acq

path 0. M_HARDWARE_PORT8; Digitizer device #: M_DEV0; Trigger controller: 0 on acq path 0. |

||

| Timer information | Timer: M_TIMER3; Digitizer device #: M_DEV0; | ||

| Hardware manual signal name | P0_TTL_AUX_IO_0 | ||